void App_Common_Init(Gpu_Hal_Context_t *phost)

{

Gpu_HalInit_t halinit;

uint8_t chipid;

Gpu_Hal_Init(&halinit);

Gpu_Hal_Open(phost);

Gpu_Hal_Powercycle(phost,TRUE);

/* FT81x will be in SPI Single channel after POR

If we are here with FT4222 in multi channel, then

an explicit switch to single channel is essential

*/

Gpu_HostCommand(phost,0x68);

Gpu_Hal_Sleep(300);

Gpu_HostCommand(phost,GPU_EXTERNAL_OSC);

Gpu_81X_SelectSysCLK(phost, GPU_SYSCLK_72M);

Gpu_Hal_Sleep(100);

Gpu_HostCommand_Ext3(phost, 0x71| (0x14 << 10)|(0x02 << 8)); //pullup in powerdown

Gpu_HostCommand_Ext3(phost, 0x71| (0x15 << 10)|(0x02 << 8));

Gpu_HostCommand_Ext3(phost, 0x71| (0x16 << 10)|(0x02 << 8));

Gpu_HostCommand_Ext3(phost, 0x71| (0x17 << 10)|(0x02 << 8));

Gpu_HostCommand_Ext3(phost, 0x71| (0x18 << 10)|(0x02 << 8));

Gpu_HostCommand_Ext3(phost, 0x71| (0x19 << 10)|(0x02 << 8));

Gpu_HostCommand_Ext3(phost, 0x43); // go to powerdown

Gpu_Hal_Sleep(100);

Gpu_HostCommand(phost,GPU_ACTIVE_M);

Gpu_Hal_Sleep(300);

Gpu_Hal_Wr32(phost, REG_FREQUENCY, 72000000);

uint32_t freq = Gpu_Hal_Rd32(phost, REG_FREQUENCY);

/* read Register ID to check if chip ID series is correct */

chipid = Gpu_Hal_Rd8(phost, REG_ID);

while(chipid != 0x7C)

{

chipid = Gpu_Hal_Rd8(phost, REG_ID);

Gpu_Hal_Sleep(100);

}

/* read REG_CPURESET to confirm 0 is returned */

{

uint8_t engine_status;

/* Read REG_CPURESET to check if engines are ready.

Bit 0 for coprocessor engine,

Bit 1 for touch engine,

Bit 2 for audio engine.

*/

engine_status = Gpu_Hal_Rd8(phost, REG_CPURESET);

while(engine_status != 0x00)

{

engine_status = Gpu_Hal_Rd8(phost, REG_CPURESET);

Gpu_Hal_Sleep(100);

}

}

Gpu_Hal_Wr16(phost, REG_PWM_HZ,10000);

Gpu_Hal_Wr8(phost, REG_PWM_DUTY,128);

uint16_t pwmHz = Gpu_Hal_Rd16(phost, REG_PWM_HZ);

Gpu_Hal_Wr16(phost, REG_PCLK_FREQ, DispPLCLKFREQ);

Gpu_Hal_Wr8(phost, REG_PCLK_2X, DispPCLK2x);

/* configuration of LCD display */

Gpu_Hal_Wr16(phost, REG_HCYCLE, DispHCycle);

Gpu_Hal_Wr16(phost, REG_HOFFSET, DispHOffset);

Gpu_Hal_Wr16(phost, REG_HSYNC0, DispHSync0);

Gpu_Hal_Wr16(phost, REG_HSYNC1, DispHSync1);

Gpu_Hal_Wr16(phost, REG_VCYCLE, DispVCycle);

Gpu_Hal_Wr16(phost, REG_VOFFSET, DispVOffset);

Gpu_Hal_Wr16(phost, REG_VSYNC0, DispVSync0);

Gpu_Hal_Wr16(phost, REG_VSYNC1, DispVSync1);

Gpu_Hal_Wr8(phost, REG_SWIZZLE, DispSwizzle);

Gpu_Hal_Wr8(phost, REG_PCLK_POL, DispPCLKPol);

Gpu_Hal_Wr16(phost, REG_HSIZE, DispWidth);

Gpu_Hal_Wr16(phost, REG_VSIZE, DispHeight);

Gpu_Hal_Wr16(phost, REG_CSPREAD, DispCSpread);

Gpu_Hal_Wr16(phost, REG_DITHER, DispDither);

//Gpu_Hal_Wr16(phost, REG_OUTBITS, 0x1b6);

/* GPIO configuration */

#if defined(FT81X_ENABLE)

Gpu_Hal_Wr16(phost, REG_GPIOX_DIR, 0xffff);

Gpu_Hal_Wr16(phost, REG_GPIOX, 0xfc00);

#else

Gpu_Hal_Wr8(phost, REG_GPIO_DIR,0xff);

Gpu_Hal_Wr8(phost, REG_GPIO,0xff);

#endif

Gpu_ClearScreen(phost);

/* after this display is visible on the LCD */

Gpu_Hal_Wr8(phost, REG_PCLK,DispPCLK);

phost->cmd_fifo_wp = Gpu_Hal_Rd16(phost,REG_CMD_WRITE);

}

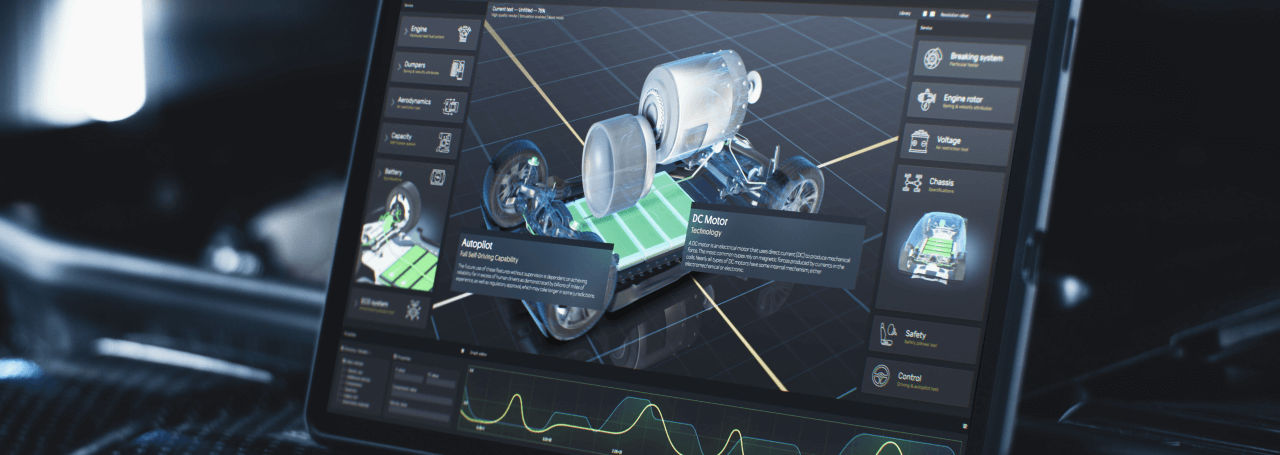

DISCOVER OUR

Whitepaper

Achieve the perfect user-display interaction with the right Touch Sensor IC. Ever faced issues with phantom touch events or certification? Boost your R&D like a pro with our Whitepaper!