void App_Common_Init(Gpu_Hal_Context_t *phost)

{

Gpu_HalInit_t halinit ;

uint8_t chipid ;

Gpu_Hal_Init(&halinit) ;

Gpu_Hal_Open(phost) ;

Gpu_Hal_Powercycle(phost,TRUE) ;

/* Le FT81x sera en canal unique SPI après POR

Si nous sommes ici avec le FT4222 en multicanal, alors

un passage explicite à la voie unique est essentiel

*/

Gpu_HostCommand(phost,0x68) ;

Gpu_Hal_Sleep(300) ;

Gpu_HostCommand(phost,GPU_EXTERNAL_OSC) ;

Gpu_81X_SelectSysCLK(phost, GPU_SYSCLK_72M) ;

Gpu_Hal_Sleep(100) ;

Gpu_HostCommand_Ext3(phost, 0x71| (0x14 << 10)|(0x02 << 8)) ; //récupération en cas d'arrêt de l'alimentation

Gpu_HostCommand_Ext3(phost, 0x71| (0x15 << 10)|(0x02 << 8)) ;

Gpu_HostCommand_Ext3(phost, 0x71| (0x16 << 10)|(0x02 << 8)) ;

Gpu_HostCommand_Ext3(phost, 0x71| (0x17 << 10)|(0x02 << 8)) ;

Gpu_HostCommand_Ext3(phost, 0x71| (0x18 << 10)|(0x02 << 8)) ;

Gpu_HostCommand_Ext3(phost, 0x71| (0x19 << 10)|(0x02 << 8)) ;

Gpu_HostCommand_Ext3(phost, 0x43) ; // passer à la mise hors tension

Gpu_Hal_Sleep(100) ;

Gpu_HostCommand(phost,GPU_ACTIVE_M) ;

Gpu_Hal_Sleep(300) ;

Gpu_Hal_Wr32(phost, REG_FREQUENCY, 72000000) ;

uint32_t freq = Gpu_Hal_Rd32(phost, REG_FREQUENCY) ;

/* lire le registre ID pour vérifier si la série d'ID de puce est correcte */

chipid = Gpu_Hal_Rd8(phost, REG_ID) ;

while(chipid != 0x7C)

{

chipid = Gpu_Hal_Rd8(phost, REG_ID) ;

Gpu_Hal_Sleep(100) ;

}

/* lire REG_CPURESET pour confirmer le retour de 0 */

{

uint8_t engine_status ;

/* Lire REG_CPURESET pour vérifier si les moteurs sont prêts.

Bit 0 pour le moteur du coprocesseur,

Bit 1 pour le moteur tactile,

Bit 2 pour le moteur audio.

*/

engine_status = Gpu_Hal_Rd8(phost, REG_CPURESET) ;

while(engine_status != 0x00)

{

engine_status = Gpu_Hal_Rd8(phost, REG_CPURESET) ;

Gpu_Hal_Sleep(100) ;

}

}

Gpu_Hal_Wr16(phost, REG_PWM_HZ,10000);

Gpu_Hal_Wr8(phost, REG_PWM_DUTY,128) ;

uint16_t pwmHz = Gpu_Hal_Rd16(phost, REG_PWM_HZ) ;

Gpu_Hal_Wr16(phost, REG_PCLK_FREQ, DispPLCLKFREQ) ;

Gpu_Hal_Wr8(phost, REG_PCLK_2X, DispPCLK2x) ;

/* configuration de l'écran LCD */

Gpu_Hal_Wr16(phost, REG_HCYCLE, DispHCycle) ;

Gpu_Hal_Wr16(phost, REG_HOFFSET, DispHOffset) ;

Gpu_Hal_Wr16(phost, REG_HSYNC0, DispHSync0) ;

Gpu_Hal_Wr16(phost, REG_HSYNC1, DispHSync1) ;

Gpu_Hal_Wr16(phost, REG_VCYCLE, DispVCycle) ;

Gpu_Hal_Wr16(phost, REG_VOFFSET, DispVOffset) ;

Gpu_Hal_Wr16(phost, REG_VSYNC0, DispVSync0) ;

Gpu_Hal_Wr16(phost, REG_VSYNC1, DispVSync1) ;

Gpu_Hal_Wr8(phost, REG_SWIZZLE, DispSwizzle) ;

Gpu_Hal_Wr8(phost, REG_PCLK_POL, DispPCLKPol) ;

Gpu_Hal_Wr16(phost, REG_HSIZE, DispWidth) ;

Gpu_Hal_Wr16(phost, REG_VSIZE, DispHeight) ;

Gpu_Hal_Wr16(phost, REG_CSPREAD, DispCSpread) ;

Gpu_Hal_Wr16(phost, REG_DITHER, DispDither) ;

//Gpu_Hal_Wr16(phost, REG_OUTBITS, 0x1b6) ;

/* Configuration GPIO */

#if defined(FT81X_ENABLE)

Gpu_Hal_Wr16(phost, REG_GPIOX_DIR, 0xffff) ;

Gpu_Hal_Wr16(phost, REG_GPIOX, 0xfc00) ;

#else

Gpu_Hal_Wr8(phost, REG_GPIO_DIR,0xff) ;

Gpu_Hal_Wr8(phost, REG_GPIO,0xff) ;

#endif

Gpu_ClearScreen(phost) ;

/* après que cet affichage soit visible sur l'écran LCD */

Gpu_Hal_Wr8(phost, REG_PCLK,DispPCLK) ;

phost-cmd_fifo_wp = Gpu_Hal_Rd16(phost,REG_CMD_WRITE) ;>

}

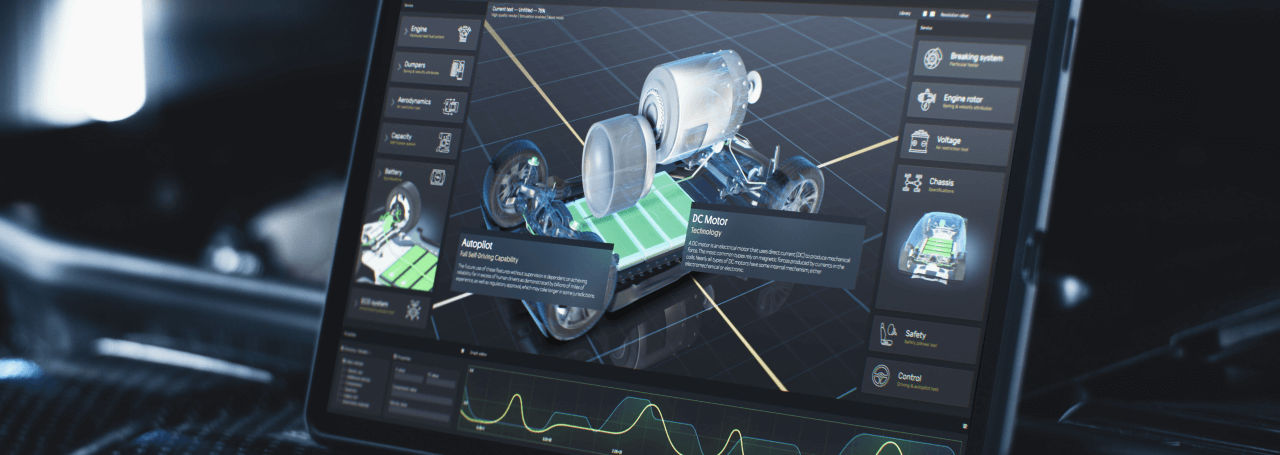

DÉCOUVREZ NOTRE

Livre blanc

Réalisez l’interaction parfaite entre l’utilisateur et l’écran avec le bon circuit intégré pour capteur tactile. Vous avez déjà été confronté à des problèmes d’événements tactiles fantômes ou de certification ? Boostez votre R&D comme un pro grâce à notre livre blanc !